UHD SDI IP

UHD SDI IP

UHD SDI IPとは

UHD SDI IPはSociety of Motion Picture and Television Engineers (SMPTE)によって定められた規格をサポートするSerial Digital Interface(SDI)のIPです。

本IPではHD-SDI, 3G-SDI, 6G-SDI, 12G-SDIをサポートします。

サポートする規格

- SMPTE ST 292-1 (HD-SDI)

- SMPTE ST 424 (3G-SDI)

- SMPTE ST 425 (3G Level-A/B)

- SMPTE ST 2081-1 (6G-SDI)

- SMPTE ST 2082-1 (12G-SDI)

サポートする機能

- Line Number (LN)パケットのエンコード/デコード

- CRCパケットの生成、挿入及びチェック

- Video Payload Identification (VPID)パケットのエンコード/デコード

- スクランブルとNRZIのエンコード/デコード

- 3G(HD)-SDI、6G-SDI、12-SDIモードの動的な変換

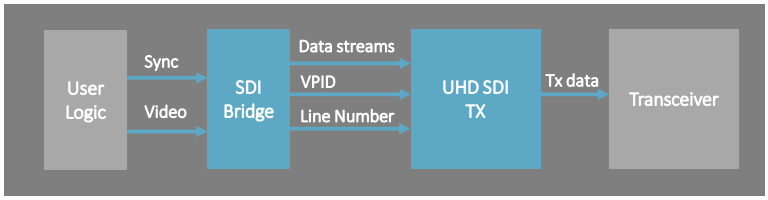

UHD SDI TX 概要

SDI BridgeはUHDとFHD出力をサポートし、多くのフレームレートと3G-SDI Level B、FHD インターレースを含む、さまざまなSDIフォーマットのマッピングをサポートします。SDI BridgeはユーザーロジックからのVideoデータをSDI Data Streamに変換し、UHD SDI TX IPに供給します。SDI Bridge IPとUHD SDI TX IPの組み合わせ使用することにより、最適なシステムを簡単に構築できます。

リソース使用量

| SDI Standard | FFs | SRLs | ADDs | LUTs | COMB4s | RAMs | DSPs |

Fmax [MHz] |

| 12G-SDI | 2838 | 0 | 216 | 2839 | 0 | 0 | 0 | 244 |

|---|---|---|---|---|---|---|---|---|

| 6G-SDI | 1278 | 0 | 108 | 1332 | 0 | 0 | 0 | 203 |

| 3G(HD)-SDI | 623 | 0 | 54 | 603 | 0 | 0 | 0 | 289 |

* Synthesis result of Efinity 2024.2(Ti375N1156)

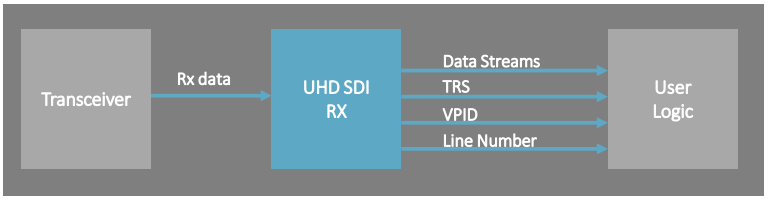

UHD SDI RX 概要

UHD SDI RX IPはトランシーバを経由して受信したデータをSMPTE規格に従ってデコードし、同期信号(TRS)、ライン番号、VPIDを抽出します。SDIの転送レートにより、出力するデータストリーム数は8(12G-SDI), 4(6G-SDI), 2(3G/HD-SDI)に切り替わります。また3G-SDIのLevel-AとLevel-B、12G/6G-SDIのtype1とtype2のマッピングを自動的に検出します。

リソース使用量

| SDI Standard | FFs | SRLs | ADDs | LUTs | COMB4s | RAMs | DSPs |

Fmax [MHz] |

| 12G-SDI | 3966 | 32 | 164 | 10222 | 0 | 0 | 0 | 198 |

|---|---|---|---|---|---|---|---|---|

| 6G-SDI | 1992 | 16 | 91 | 3386 | 0 | 0 | 0 | 212 |

| 3G(HD)-SDI | 991 | 8 | 53 | 1150 | 0 | 0 | 0 | 186 |

* Synthesis result of Efinity 2024.2(Ti375N1156)

サポート

CISには各種高速インターフェースや画像処理に関連したRTL設計、高速信号を含む基板設計、組み込みソフト開発などの分野で経験豊富なエンジニアが多数在籍しております。

IPのカスタマイズ、Efinix社以外のFPGA対応についてもお気軽にお問い合わせください。